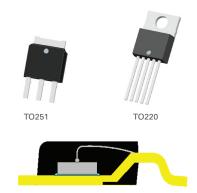

# TO

## **Transistor Outline**

Transistor Outline (TO) packages are capable of supporting high pwer devices including diodes, thyristors, power mosfet, insulated gate bipolar transistors and other power devices. They are available in many body sizes ranging from  $3.0 \times 3.0$  to  $18.04 \times 7.52$ . Pin counts range from 2 to 6.

#### **Highlights**

- High current/voltage capacity (200A/2000V)

- Low switching loss

- High thermal conductivity

- Lead-free application

- SiC / GaN wafers

#### **Features**

- High power and electrical dissipation

- Package body sizes range from 3.0 x 3.0 to 18.04 x 7.52

- Pin counts from 2 to 6

- Heatsink compatible

#### **Standard Materials**

• Leadframe: Cu / Ag plating / Selective Ag plating /

Selective Ni plating

Wire: Cu / Au / Al / Al ribbon

• Epoxy: Conductive / Lead Tin Alloy Silver / Solder Paste

• Compound: Green / Non-green molding compound

Lead Finish: Sn plating

### **Process Highlights**

Package Thickness

Die Thickness

Wire

Lead layer

0.95 - 5mm

Minimum of 70um

Cu / Au / Al wire/ribbon options

Single Layer / Dual Layer

#### **Package Level Reliability**

• Moisture Sensitivity Level

• Temperature Cycling

PCT

THT

HTST

MSL 1/2/3 @ 260C

-65C to 150C, Dwell= 15 min,

500 cycles

121C/100%RH/205 Kpa, 168 hrs

85C, 85%RH, 1008hrs

Ta=150C, 1008hrs

## **Applications**

- Computing

- Industrial

- Consumer electrical

- Networking devices